Cell phone cpu transistor count9/28/2023 One of the metrics used for determining how good a semiconductor process is relates to how many transistors per square millimeter are in a standard chip made on that process. The Ultimate Metric: Transistors Per mm 2 The nearest would be Broadwell, at 82 mm 2, but this chip also had a lower proportion of integrated graphics compared to Skylake and newer. This qualifies as a 2+2 design.įor comparison to Intel’s previous dual core designs, this marks Intel’s smallest dual-core design to date. This chip does indeed have two Cannon Lake CPU cores, and 40 Gen10 execution units on the integrated graphics, although the graphics are disabled. This photo of the chip in the system (with IO die on the right) gives a die area of 70.52 mm 2, well within an acceptable margin of error. It turns out we weren’t too far off on the die area.

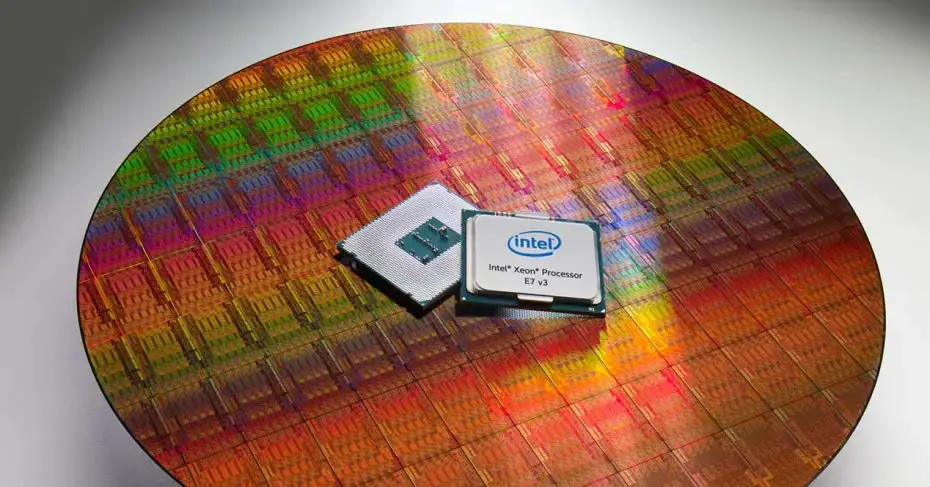

Photo: Techinsights, Measurements by WikiChip After the Lenovo Ideapad was made available in China, the experts at TechInsights got hold of a unit and took their saws to the design. Intel presented a full 300mm wafer of Cannon Lake 10nm chips, and through luck we were able to get some clear definition of the chips.īased on this wafer, we estimated that the chip would be around 70.5 mm2 of die area, and at the time we assumed this was a dual core design with ‘GT2’ graphics, the standard graphics configuration. The first true glimpse of a physical Cannon Lake chip, beyond the brief showing of what was supposedly an early Cannon Lake laptop at CES 2017, was during the Chinese version of Intel’s Technology and Manufacturing day in September 2017. I highly recommended several of his articles, including his write-ups from IEDM 2017, ISSCC 2018, IEDM 2018, and his page on Cannon Lake. This page uses his material extensively as the primary source.

Many thanks to David Schor of WikiChip for his articles on Intel’s 10nm.

0 Comments

Leave a Reply.AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed